Raltron晶振公司常見的感應振蕩器技術(二)

上一篇我們講了倒置臺面晶體和水晶選擇等內容,初步了解了Raltron晶振的頻率控制元器件技術研究,在晶體這個領域歐美國家始終比較在行,并且目前仍然還在不斷的開發和科研。Raltron公司面向的客戶群體主要有無線通信,汽車制造,廣播音頻,數碼電子,全球導航定位系統,工業儀器等模塊。不僅為來自各個地區的用戶提供品質好的晶振產品,還為客戶解決一系列晶體/振蕩器相關的難題,提供適用的晶振解決方案,為每一位客戶排憂解難!

帶狀水晶系列:

ASIC CELLS振蕩器基礎。今天使用最廣泛的振蕩器是MOS門振蕩器使用無緩沖逆變器。幾乎所有的微處理器都在與許多其他數字應用程序一樣這個電路內置在電池內或被驅動來自使用該ASIC的外部振蕩器電路。

石英晶體振蕩器單元具有幾個特征這對振蕩器設計師很重要。Rin Rin高-10兆歐姆擊潰。Rout取決于邏輯類型正在使用。ECL邏輯具有低阻抗-在7歐姆的范圍內。CMOS邏輯有更高的輸出阻抗-在700歐姆。HCMOS邏輯通常是介于250和500歐姆之間。一個振蕩器設計師應該獲得輸出來自的阻抗信息制造商。如果沒有這個信息可用,簡單的輸出阻抗測試。

電路如圖2所示。獲得。通過偏置逆變器得到增益在線性模式下。偏見是通過連接逆變器的電阻器輸出到輸入。此連接導致高增益和寬帶寬,但都缺乏一致性。

相移:

f0處的相移,頻率振蕩大約是180度通過放大器從輸入到輸出。導出額外的180度相位來自pi反饋網絡。保險可靠的啟動和穩定的運行,電路必須具有相移的能力比180更遠20度學位最低反饋要求。

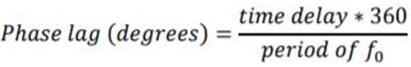

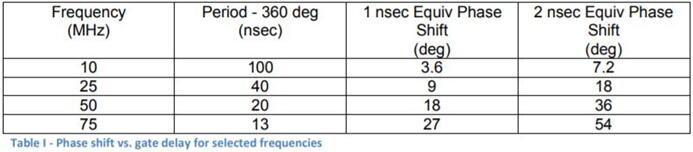

通過時間延遲修改相移從放大器的輸入到輸出-通常為1至2納秒。以來頻率是時間,時間的倒數延遲等于額外的相移逆變器。外部pi電路必須比延遲小180度等同移位。表I顯示了1和2的相移選定頻率下的納秒延遲。這種減少的相移信息將是在波德圖分析中很有用。

設計師應該確保有足夠的動態范圍來彌補元件或電源變化。對于例如,電路中的手指會打擾相移并允許石英晶振啟動,鎖定繼續,并繼續振蕩。為了滿足巴克豪森的相移標準,我們必須在外部移動180度(加上一個至少25個附加度)反饋回路。設計穩定振蕩器,希望具有快速的相位變化率在180度點。在整個過程中獲得180度相移pi網絡,我們需要相移90水晶兩端的度數。在ASIC輸入側的晶體,晶體流入C1的電流如果變為90度津很高。在ASIC輸出端晶體,應該進行相移通過90度,效果較差從逆變器的時間延遲相移-參考表1。基本反饋電路。一個基本的皮爾斯OSC晶振電路如圖3所示。組件包括相移元素C1和C2以及輸出阻抗調節電阻,Rx。注意Rx是分立電路元件而不是包含在輸出阻抗中逆變器。如果振蕩器設計中省略了Rx(不幸的是很多次),容易出現問題。設計師應該總是為這個組件布置他的電路如果Rx是,則使用零歐姆電阻(短路)他的反饋配置不需要。反饋元素選擇。為了這紙,ASIC單元外部的反饋將被縮減為“pi”或平行坦克組態。值得注意的是“T”配置有類似的特點但是不屬于本文范圍。那里是四(4)種可能的組合非負載可能發生的電抗坦克電路。這四個案例是如圖4所示。

圖4,情況1,兩腿都有電容器和相互連接的電感器。該電路只有在電感器振蕩時才會振蕩放在Z3的位置。一個例子案例1是常見的Pierce配置常用于有源晶振電路。連接晶體可以滿足振蕩要求條件略高于每個晶體上的Fs模式。電路將捕獲模式具有最低的實際期限。大多數時候頻譜,晶體是電容性和無振蕩。

電抗與參考圖5晶體諧振器的頻率響應。如果a,則情況2和3都不能振蕩電容器或電感器是外部的是連接的。如果是電容器,情況4可以振蕩連接在終端之間。水晶的連接可能不是因為晶體的電抗是有效的大部分頻率都是電容性的光譜。振蕩可以在多個時發生因為晶體可以滿足頻率所需阻抗均低于Fs和以上法。在這方面一定要小心組態。

阻抗匹配。振蕩器電路取決于階段的變化率穩定性。階段性變化的重要性可以用圖形方式看到當考慮到頻率的變化時擾動,組件變化,潮濕,上帝的行為等。振蕩器會不滿足巴克豪森的階段標準舊的頻率,所以它改變階段,直到振蕩可能發生。假設不穩定電路轉換階段2度。這可能導致頻率改變為6Hz或相位斜率為1/3度/Hz。通常,我們希望進口晶振每Hz的相位斜率為40度。如果在輸入端進行阻抗匹配并且輸出pi網絡,相位斜率大大降低了因此,設計師應該爭取一個大的不匹配最大化相位斜率。這一切都必須完成控制中的常識。作為阻抗匹配的一個例子,考慮在110中插入一個電容器伏墻插座和試圖移動電力公司的階段。顯然,這個不起作用,因為信號源有非常非常低的阻抗。如果是一個系列插入電阻器的電阻相等對電容器的電抗,相位在R-C處換檔為45度結和信號幅度將是減少½。

同樣的現象發生在ASIC的輸出。如果歐美晶振輸出阻抗與外部電抗相比較低,電容器不會明顯偏移相。陳述更簡單,一個小C2連接到低阻抗輸出ASIC什么都不做。如果添加Rx,則(Rx=XC2)45度相移將發生在水晶。可能是最重要的本文的考慮是選擇C2相對于輸出阻抗ASIC單元。參考圖6。觀察到如果Rx是短路,則Rout是直接的與C2并行。輸出的Q值匹配網絡定義為Rout+Rx除以XC2。教科書需要Q版10.考慮妥協并讓Q≈僅2.如果上述電路工作在40MHz和單元具有輸出阻抗200歐姆,C2應該是39pf-不是不合理。如果ECL門與a一起使用Q為1,C2應為560pf-即不合理。

使用戴維寧相當于輸出司機,人們可以認識到這個階段在輸出端移位-C2連接非常多一個函數C2的選擇。使用相當于Norton,我們觀察到了輸出阻抗直接跨C2。底線。如果Q小于2,則增加Rx或增加C2-在限制范圍內。接受Q.最低=2。最低Q=5的設計。ASIC驅動能力。驅動器必須具備ASIC單元的能力考慮選擇組件。該電容器電流(i)=dQ/dt,因此Q=∫I*DT。然后電壓是積分I*DT/℃。輸出驅動程序必須能夠在短時間內充電C2。如果C2是小,它可以很快充電;但是,如果C2更大,ASIC輸出驅動器具有限制gm,電容器不會充電顯著和電壓發展C2將非常有限。

來自電池的輸出信號不僅如此從外部驅動C2,但也是一樣的信號驅動下一個內部邏輯用于生成系統的元素時鐘信號。如果這個信號很小的話振幅,應引起關注。邏輯電平應從20%切換到80%在ASIC的輸出端的VDD。如果在輸出處觀察到小信號ASIC*,有兩種方法增加信號電平-減少負載(電容)C2或增加值RX。如果選擇Rx的值等于XC2,諧振器處的信號幅度為½信號進入系統時鐘。該添加Rx會降低晶體驅動電平,降低EMI并增加相移從而產生更高的可靠性,更穩定系統。

手機版

手機版