Raltron晶振公司常見的感應振蕩器技術(三)

布置晶體和振蕩器單元的振蕩電路是比較復雜的,需要掌握相關的理論知識,和實操經驗,以及會算了公式看懂公式,在這方面Raltron晶振公司做得比較好,注意石英水晶的研發,每年都投入大筆的金錢做為科研費用,并因此也為集團帶來高收益。金洛鑫電子這幾篇文章,都著重講了晶振的感應振蕩器技術,分為四篇,這是第三篇,最后一部分將會在下周一為大家獻上。

在講到振蕩器的電路及相關資料的時候,總會提到電阻,電壓,阻力,CL,電容,Q值,輸出等詞,這些都是振蕩器電路上常見的專業術語,你可以在任何關于石英晶體振蕩器的文章中可以看到,接下來也會圍繞著這幾個中心點,讓大家更熟悉振蕩器電路。

底線:設計大信號

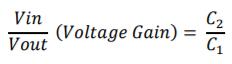

ASIC輸出- 4伏特p-p,用于5伏邏輯。僅使用FET探頭測量信號。從輸出到輸入的電壓增益。從輸出反饋的電壓電平通過被動元件輸入可能小于或大于信號輸出。乍一看,這可能聽起來很奇怪該信號可以通過增加被動元素;但是,如果門輸入具有高阻力,可以證明輸出信號正在為水箱上的水龍頭充電電路和無源電壓增益是大約等于C2/C1。

為了驗證被動增益現象,在上放置一個非加載范圍探針輸入單元格(與C1相同)。去掉C1。觀察信號增加直到ESD二極管限制信號。底線:彌補信號損失通過晶振,選擇:

![]()

反饋電阻。反饋電阻用于偏置逆變器的輸入A類配置。的大小電阻應足夠大以防止加載反饋網絡并允許逆變器在其中心運行范圍。

對于基本模式和泛音帶有儲能電路的振蕩器,R1應該是高頻時0.5到1.0兆歐姆在較低的1至5兆歐姆頻率。對于無感應器的第三泛音,選擇更重要,只有少數幾個千歐姆。

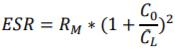

指定石英晶體。系列還是并聯?平行!抵抗性。低晶體電阻期望更好的穩定性和更高的可靠性。低電阻晶體也是與成本成反比。對于并聯諧振晶體,電阻應指定為有效系列阻力(ESR)。

其中Rm是運動阻力,C0是靜電電容和CL是負載抵抗性。底線:阻力應該是指定盡可能低,實際上可能包括經濟因素。負載電容。對于并聯共振晶體,負載電容必須指定-假設您知道負載。這不是“首先出現的-坑洼或輪子?“情景。振蕩器設計應該指明什么類型應購買組件。該訂購或庫存的水晶不應該決定振蕩器設計。

雖然CL選擇的更多細節是在下一節中,水晶是一般指定為12至20pf,CL這種類型的應用程序。振蕩器設計細節。警告。以下元素值是建議可能需要的起始值迭代并要求測試。

測試。測試應該在a上進行模擬最終產品的面包板。應用啟動電壓應該包括緩慢的上升和步驟功能(這可能需要刪除PCB供電電壓并施加VDD外部可變電源)。在電源緩慢斜坡測試期間泛音,人們可以期待這種操作將是基本的,直到供應達到約2.5伏特。更正

較低模式啟動通常由降低C2的電容值。兩者的電源步進功能測試基本和泛音設計需要瞬間施加電力。這個可以通過提升ASIC VDD引線來完成并將其接觸到VDD。這個測試應該包括ASIC的所有電壓絕對最大值-通常為7.0伏特。

在高壓階躍功能測試期間,石英振蕩器可能會嘗試跳到下一個更高的模式。這是不可接受的條件。更正通常包括增加C2的價值。

負載電容。負載電容是指定為放置的電容與水晶的引線平行,會導致振蕩器工作在f0。PCB流浪電容和ASIC輸入/輸出電容有助于負載。

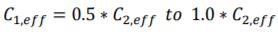

C1和C2彼此串聯。計算C1和C2需要雜散電容必須添加到所有計算。典型的配置有大約10pf的雜散電容輸入和輸出。對于初稿,計算負載電容沒有任何流浪的住宿,輸入或輸出電容。如果設計C1和C2的計算指定10pfCL,使用15微升水晶。C1和C2將使用5pf計算假設。

共通電路選擇。圖7顯示6種用于ASIC貼片晶振的常見設計振蕩器操作。第一個電路(A)用于基礎- AT和BT削減。電路(B)是首選弦外之音。偶爾使用電路(C)(D)和(E)-但不是本作者推薦的。

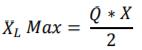

電路(F)是(B)最高的替代如果(B)的驅動程序是泛音頻率有限。基本模式設計。該基模振蕩器的操作電路中顯示(A)一直很好記錄(4),(5)和(6)。建議值列于表II中。可以理解無電感器方法通過觀察分流的影響具有低值電阻的貼片石英晶振。一個并聯諧振電路,電感和電阻具有電抗阻力圖如圖8所示那個電路的最大電感可以產生-3dB點并且有一個的價值。

并聯諧振電路的Q是定義為并聯電阻除以要么是電抗:

![]()

重新排列:XL Max=R/2。在圖9中,并聯諧振電路的電感器取而代之的是晶體的電感。為2個分流值生成一個圖抵抗性。我們觀察到我們可以縮小圓的直徑,因此最大可達到的電感值。

抑制基本模式和在3號操作,分流電阻(R1)必須降低。圖10說明了用途一個2000歐姆的分流電阻器晶體,帶5pf負載電容。注意矢量“B”在10MHz時為-j3000歐姆。晶體的電抗無法提供+j3000歐姆(極限為R1/2),如圖所示矢量“A”是相同的幅度和與矢量“B”相反的相位。振蕩根本不會發生。

對于第3次泛音,現在加載相同的5pf具有-j1000歐姆,如矢量“D”所示。矢量“C”具有相反的相位相同的幅度。現在是巴克豪森的階段標準已得到滿足和振蕩器只能在f0=30MHz下運行。

負載的電容電抗會在第三個泛音減少1/3;該需要的感應電抗量也減少了1/3。如果巴克豪森的階段標準要求a從諧振器給出感應電抗在基本模式下運行,并且適當值電阻并聯放置用水晶,它會減少量感應電抗低于期望值由負載電容建立。

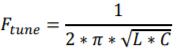

系列陷阱的泛音。泛音帶有系列陷阱的振蕩器是皮爾斯組態。基本陷阱是一個額外的系列L/C電路位于輸入或單元格的輸出。該系列引起共鳴組件是從基本計算的方程:

陷阱位置的選擇是可選的。如果找到在單元格的輸入端,Q值會很高-實際上是電感器的Q值。如果陷阱Q將位于單元格的輸出上低-有效輸出阻抗細胞+Rx除以細胞的電抗電感器。在輸出上定位陷阱也傾向于在它之前清理信號進入水晶。

如果陷阱是,轉動陷阱是非常關鍵的在單元格輸入中。電感器通常是±10%的值。確定陷阱是適當調諧,電容應該是可調。確保陷阱保持調整過溫,電容應該有負溫度系數等于電感的那個。可能是一個小電阻與電感串聯添加以降低Q到20并消除了這些問題。

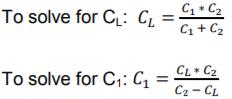

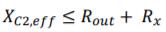

現在是“有效電容”一詞適用于輸入或輸出腿系列陷阱。注意上面的共振,a系列陷阱變得歸納并且在與C1并行。電壓增益現在C2,eff/C1表示輸出端的陷阱或C2/C1,eff對于輸入腿的陷阱。單元輸出具有標準Rx相位移位電阻。C2遵循輸出阻抗規則表IV和V是建議值。

平行坦克的泛音。該帶有并聯槽的泛音石英晶體振蕩器也是皮爾斯配置,細胞輸出具有標準的Rx可選相移電阻,必須使用電阻計算電抗油箱腿的有效電容。

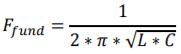

并聯反諧振電路可以是位于輸入或輸出中細胞。通常情況下,更好的選擇輸出(最好過濾不需要的模式在水晶之前)。并聯共振電路應調整為25%至50%兩者之間的頻率距離基本和第三個泛音。如果調整到更接近基頻,電路將更有效第三次泛音頻率的電容。如果調整得更接近中途距離,那么電路將具有更高的增益并且更容易啟動。并聯諧振元件是根據基本方程計算表IV和V是建議值。

注意:該電路在許多情況下也是可以接受的五泛音設計。BODE PLOT ANALYSIS。分析選擇的反饋電路被執行使用微帽電路分析程序。圖11,12和13是圖的曲線圖無電感泛音器(圖7,電路B)在50MHz。圖14是相同的晶體電路F.圖15和16是電路F.30MHz。圖11顯示了對值的響應表III,在50MHz下具有25歐姆晶體。對于具有1納秒延遲的逆變器,相位需要換檔是180-18或162度。信號損耗約為4dB。

圖12顯示了更改Rx的結果到150歐姆。注意相變的變化率在162度地區更陡峭,該階段將繼續增加10度;然而損失是一個額外的2dB。圖13顯示了圖12的校正隨著C1減少到5pf。Rx還在150歐姆。這個情節非常相似原圖11.除晶體負載外計算,Rx和C1是50的交易兆赫。

圖14是電路F中的相同OSC晶振具有表VII的值。注意電路有更快的變化率,因為反饋電阻增加了。圖15顯示了40歐姆的響應,電路中的30MHz晶體F.組件除Rx為a外,其值按表VII列出短。操作點將接近180度;但是,階段性變化率不是很陡峭。信號損失很小。圖16安裝了300歐姆Rx和C1減少到10pf。注意信號丟失是大致相同;然而相移在180度時更快點。Rx和C1互換增加了收益增加的變化率。摘要。對于基礎應用程序,選擇電路“A”。對于泛音,選擇“B”或“F”。布局全部Rx的電路。大信號設計ASIC輸出。使用Rx減少信號在水晶上,防止裝載ASIC輸出。保持C2,凈值大于C1,凈值為彌補水晶損失。檢測結果。

手機版

手機版