LVDS晶振驅動多個輸入

差分晶振系列里比較常用的輸出方式是LVDS,這是一種低電壓的差分信號,主要應用于圖像輸出傳送,高速度數據通信處理,網絡程控交換等領域,它的電流傳輸數據是恒定的3.5mA,可以產生非常低的EMI消除共模噪聲干擾,因此具備LVDS輸出的石英晶體振蕩器,通常都擁有低相位噪聲性能。LVDS在輸出信號的時候會使用交流耦合技術,這樣是為了讓交流耦合電容器隔斷全部的直流分量信號,實現直流平衡,因為LVDS晶振還具備比較高端的低相位抖動功能。

本應用筆記介紹了如何將LVDS信號用于采用Virtex-EFPGA的高性能多點應用。多點LVDS允許許多接收器由一個Virtex-ELVDS驅動器驅動。仿真結果表明此處描述的參考設計將從DC運行到311Mbits/s。本應用筆記包括DC規格,微帶線和布局指南。采用簡單的源和差分端接,Virtex-EFPGA直接驅動多點LVDS,取代昂貴的TTL-LVDS驅動器和接收器,減少電路板面積和高性能應用的偏斜。

與其他LVDS驅動器相比,Virtex-E驅動器實際上提高了信號完整性通過吸收源處的任何反射能量而不是將其傳遞下來這條線。這項創新可實現多點線路上的311Mb/s信令多為20個LVDS接收器,在參考設計中跨越4英尺以上,具有高信號完整性和抗噪性。引言LVDS使用差分信號來提高單端噪聲抗擾度技術。多點LVDS允許許多接收器由一個接收器驅動Virtex-ELVDS驅動器。真正的差分LVDS輸入和輸出能力Virtex-EFPGA支持這種多點應用。Virtex-E多點降落LVDS驅動器可以驅動具有20比1扇出的線路,從而制造出Virtex-ELVDS適用于各種高負載應用。Virtex-ELVDS驅動器消除了昂貴的TTL-LVDS轉換器,實現了邏輯的直接接口高速差分信號。這種集成減少了信號偏斜和減少實現高性能應用程序所需的電路板面積。多點LVDS電路。

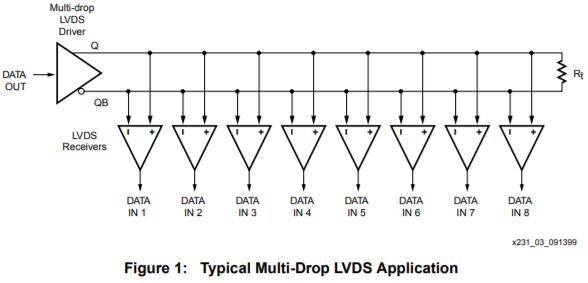

圖1顯示了典型的多點LVDS石英晶振應用。Q和Q輸出左側的LVDS驅動器串行連接到LVDS接收器的輸入沿著多點線的長度。電阻器RT終止Q和Q.在多點線路的末端并行發出信號。簡單的微帶線在具有接地層的標準PC板上制造,足以滿足此應用需求。

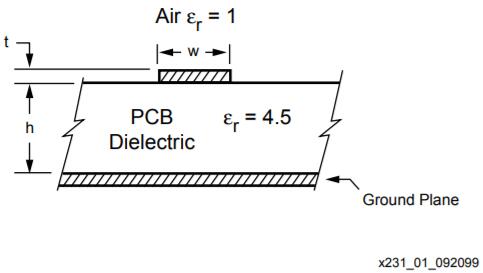

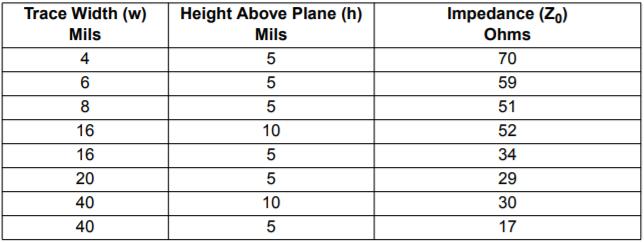

微帶線是頂部或底部的PCB(印刷電路板)跡線PCB在下一個內層的地面或電源平面上。圖2顯示微帶傳輸線的橫截面。跡線寬度(w),跡線高于地平面(h)的高度,跡線厚度(t)和相對電介質PCB的常數(εr)決定了微帶特性阻抗(Z0)。表1總結了微帶的特征阻抗圖2顯示了使用1盎司銅的FR4PCB上w和h的典型值。

圖2:微帶傳輸線的橫截面

表1:w和h的典型值的微帶阻抗

筆記:

t=1.4密耳(1盎司銅)

εr=4.5(高頻時的典型FR4)

1000密耳=1英寸=25.4毫米

阻抗誤差=±2%

平面上方的跡線寬度和高度四舍五入到最接近的密耳易于布局和制造。注意微帶傳輸線阻抗與w/h比大致恒定。w/h比率為4,給出大約Z0=29到30歐姆。w/h比為1.6,給出大約Z0=51至52歐姆。使用w/h比率近似,具有任何平面間距的微帶的特征阻抗可以是估計。

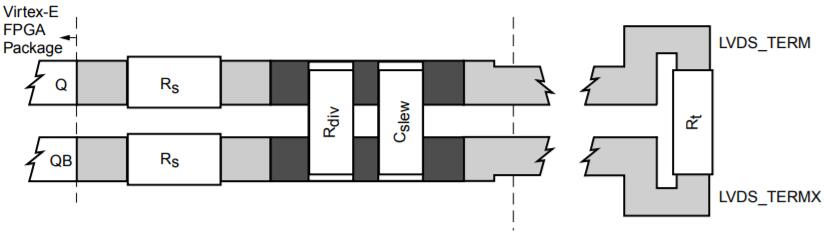

圖3是帶有源的Virtex-E多點LVDS驅動器的示例布局左邊是電阻和電容,右邊是終端電阻。

1.所示的所有PCB走線均為29Ω微帶線。

2.可以使用與Rs和Rdiv串聯的更高阻抗

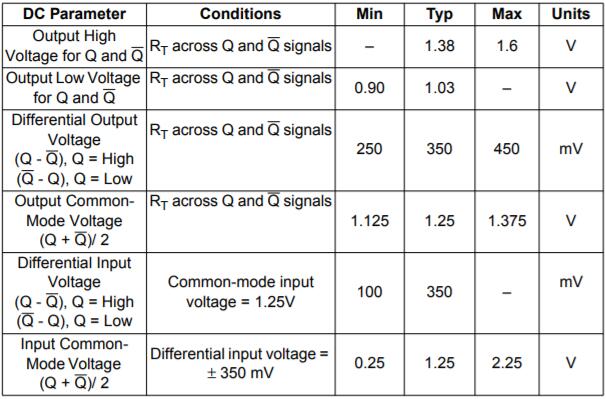

LVDS輸出通常驅動±350mV的電壓擺幅(Q-Q),并且Q和Q的平均值(Q+Q)/2有時被稱為偏移電壓或共模電壓。典型的LVDS輸出共模電壓為1.25V,由LVDS驅動程序設置。有關多點LVDS的更多信息,表2總結了DCLV DS的規格。

表2:標準LVDS DC規范

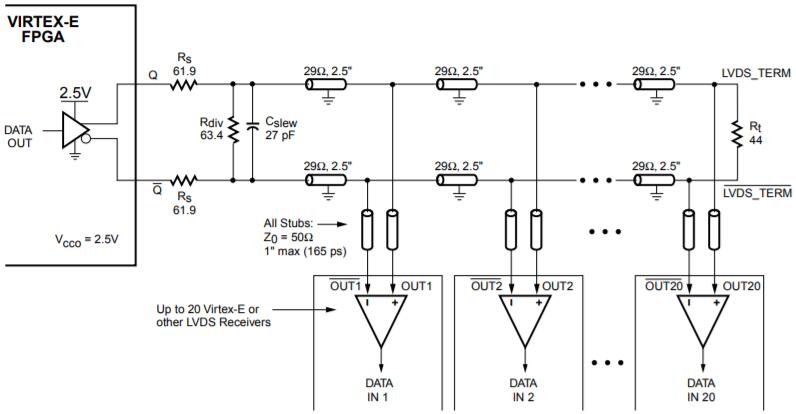

圖4顯示了Virtex-ELVDS線路驅動器的完整原理圖以多點配置驅動20個LVDS接收器。接收器是Virtex-E接收器或其他現成的LVDS接收器。LVDS信號由左側的Virtex-ELVDS驅動器驅動,并以菊花鏈形式連接兩條29歐姆的傳輸線和短截線連接到所有20個LVDS接收器OUT[1:20]和OUT[1:20]節點。每個LVDS接收器每2.5英寸輕觸主多點線路,多點線路長度為50英寸。每LVDS接收器抽頭線具有1英寸的最大短截線長度和50歐姆傳輸線對地阻抗,或差分阻抗為100兩個短截線之間的歐姆。放置一個44歐姆的終端電阻RT在靠近最終LVDS的LVDS_TERM和LVDS_TERM節點上接收器,在右邊。電阻RS和RDIV衰減輸出的信號VCCO=2.5V的Virtex-ELVDS驅動器,提供22歐姆源阻抗(串聯終端)到29歐姆傳輸線。該設計由于增加了LVDS晶振的負載,因此需要22歐姆的源阻抗接收器將29歐姆線路降至22歐姆的有效阻抗一般。電容CSLEW降低了Virtex-E的壓擺率LVDS驅動器,可以減少反射,減少接收器的振鈴。

圖4:Virtex-E20負載多點LVDS原理圖

為什么一條29歐姆的傳輸線在兩端用22端接歐姆終止?答案在于傳輸線的行為。當電容式接收器和短截線加載傳輸線時,額外的電容會降低有效阻抗。圖4中的接收器有有效負載電容約為9pF,包括接收器電容,走線和短截線電容。一個9pF電容器,每2.5英寸放置一個29歐姆線將線路降至22歐姆。因此,反射是如果線路端接到22歐姆,則最小化。有關更多信息有效的傳輸線阻抗,見霍華德W.約翰遜,“高速數字設計:黑魔法手冊,“1993,pp.172-174。關于等間距電容負載提供以下等式:

如果Z0=√L/C.

其中L=電感/單位長度

C=電容/單位長度

和CL=每個負載的電容

N=負載數量

H=傳輸線的總長度

然后Z0EFF=√L/[C+N*CL/H]

雖然傳輸線使用的阻抗比典型值低,在表2中使用的規范中發現的阻抗,所有的電壓擺幅符合LVDS標準。這意味著任何LVDS接收器都可以工作正確地在這個多點線上。實際上,較低的阻抗會導致更寬的走線,從而減少沿多點線路的電感和趨膚效應損耗。兩條29歐姆單端傳輸線可以是微帶線,帶狀線,或單端等效的58歐姆雙絞線或類似的平衡差動傳輸線。請參見Xilinx應用筆記中的附錄A.XAPP230,“LVDSI/O標準”,用于討論傳輸線和LVDS中使用的終端。多點Virtex-ELVDS線路驅動器符合所有標準ANSI/TIA/EIA-644LVDS接口標準DC輸入電平如表2所示

輸出共模電壓通常平均為VCCO/2。組件價值RS,RDIV和CSLEW的推導可以在第10頁的附錄B中找到。Virtex-ELVDS的直流性能符合或超過表2中所示的ANSI/TIA/EIA644LVDS接口標準規范。圖4中的Virtex-E多點LVDS終端與其他LVDS不同源終端,因為它實際上吸收了源處的反射能量。

雖然大多數LVDS驅動器的行為類似于具有高輸出的電流源阻抗,Virtex-E多點LVDS線路驅動器的行為類似于電流源與22歐姆電阻并聯,從而改善光源終止反射信號。22歐姆的源阻抗Virtex-ELVDS驅動器可以吸收幾乎所有的差分反射容性負載沿多點線分布,減少了站立與其他LVDS驅動器相比,波浪,下沖和噪聲水平。該LVDS_TERM和LVDS_TERM以及傳輸線上的電壓達到或超過表2中所示的所有標準LVDS輸出電平。

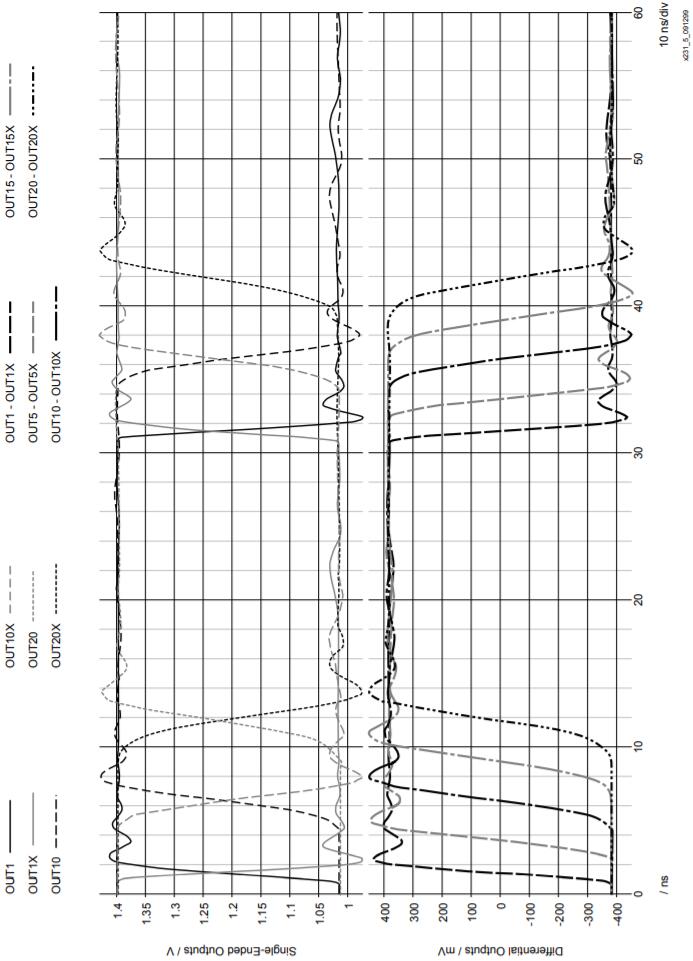

圖5顯示了Virtex-E多點LVDS驅動器的典型階躍響應對于圖4中的原理圖,上圖顯示了單端輸出1,10和20的波形,對應于輸入端的接收器多點線的開始,中間和結束。下圖顯示了沿著多點線路的五個接收器的差分電壓從開始結束。所有電壓均在接收器的片上差分輸入端測量。所有接收到的波形都顯示出類似的特征,幾乎沒有下沖或過沖和負載反射可忽略不計。

圖5:Virtex-E多點LVDS驅動器的典型階躍響應

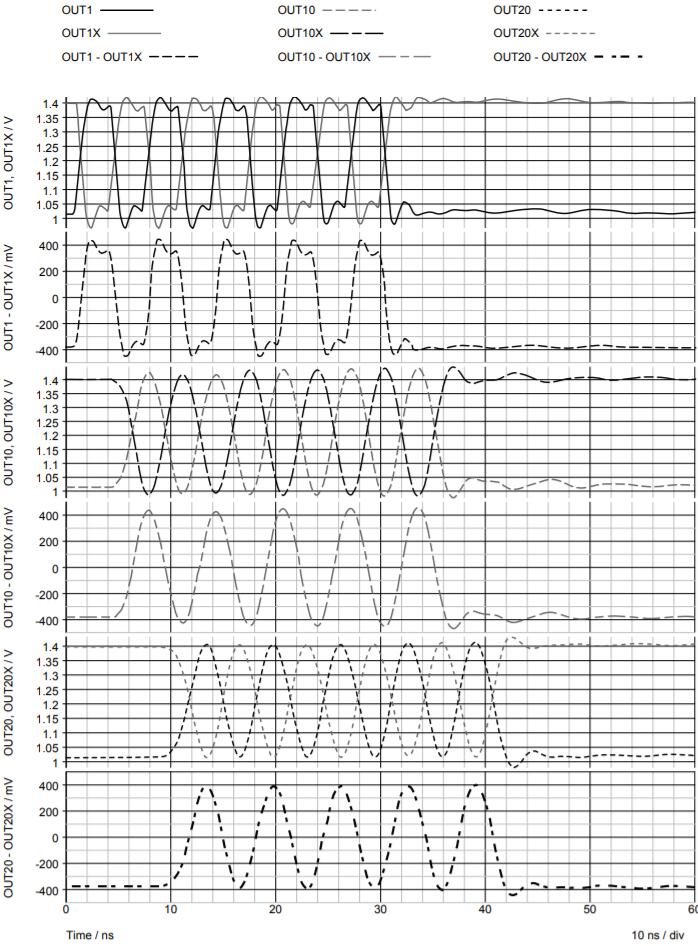

圖6顯示了典型的311Mb/s突發數據(或155.5MHz時鐘)響應Virtex-E多點LVDS輸出,用于圖4中的原理圖。單端并且沿著多點線示出了輸出1,10和20的差分波形。所有接收的波形都顯示出相似的特征,很少或沒有下沖/過沖和可忽略不計的反射。一些平滑的波形發生在接收器加載的多點線的長度上,但衰減很小。即使最后一個接收器也能看到近400mV的峰值在19個其他接收器之后的50英寸線的末端。優秀Virtex-E多點LVDS的性能可歸功于它的匹配源阻抗和源極上升時間減少電容器CSLEW。Virtex-E多點LVDS驅動器與LVDS接收器完全兼容。

圖6:Virtex-E多點LVDS輸出的典型311Mb/s突發數據響應原理圖如圖4所示。

Virtex-EFPGA發送和接收多點LVDS。最大值對于-7Virtex-E速度等級,數據速率為311Mb/s或155.5MHz的時鐘。Virtex-ELVDS驅動器可顯著改善信號完整性其他現成的LVDS驅動器由于其匹配的源阻抗而導致系列終止傳輸線并最小化源反射。可以為多達20個LVDS接收器提供可靠的數據傳輸電氣長度為8.25ns(50英寸),僅受皮膚效應損耗的限制PCB走線。采用LVDS的Virtex-EFPGA消除了昂貴的TTL-LVDS驅動器和LVDS-TTL接收器,減小電路板面積,減少信號延遲偏差,同時可靠地傳輸長距離的高速數據和時鐘芯片,電路板,機箱和外圍設備之間。

Virtex-E多點LVDS電路的印刷電路板布局指南在圖4中如下:

1)具有受控傳輸線的多層印刷電路板阻抗是必需的。

2)LVDS驅動器和接收器之間的所有傳輸線應該是參考公共地平面,除非通過平衡差分傳輸線,如雙絞線。對于雙絞線和其他平衡線,利用連接到地面的接地屏蔽在雙絞線電纜的開頭和結尾處的平面允許共模返回電流。如果沒有可用的屏蔽連接,請額外使用注意使用對稱和等長路由并確保容性負載平衡差分對以防止過多的共模差模轉換。不要在信號下分割地平面因為這會導致電感增加導致大的不連續性。

3)電阻RS和RDIV應靠近Virtex-E輸出Virtex-E多點LVDS線路驅動器。放置并聯終端電阻RT接近多點線路遠端的最終LVDS輸入。

4)電容CSLEW應靠近電阻RS和RDIV。

5)應使用多點LVDS的對稱和等長路由源和目標之間的信號對,以最大化共模拒絕。以兩個LVDS信號之間的最小間距布線兩個LVDS信號沿多點線和存根的跡線。如果跡線間距小于電介質厚度對地平面,差分阻抗的影響必須包括在內以確定有效的傳輸線阻抗跟蹤阻抗將受差分阻抗的顯著影響兩條痕跡之間。較寬的間距對阻抗的影響較小。

6)Virtex-E為驅動和提供專用的LVDS輸入/輸出對接收LVDS。從單個時鐘驅動的IOB寄存器提供了一個方便點同步輸入和輸出。

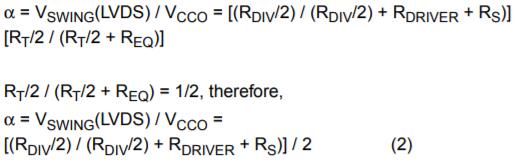

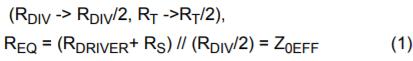

參考圖4,電阻器RS和RDIV衰減出來的信號Virtex-ELVDS驅動器提供匹配的源阻抗(串聯終止)到傳輸線。確定RS和RDIV的值通過這兩個約束。等效源阻抗REQ,包括Virtex-E驅動器阻抗RDRIVER,必須等于有效傳輸線阻抗,22歐姆。使用差分半電路:

選擇RS和RDIV以獲得所需的信號路徑衰減從Virtex-E驅動器到LVDS目的地。所需的信號衰減定義為α。

使用等式1和2并求解RDIV和RS產量:

代入Z0EFF=22歐姆,RDRIVER=10歐姆,VCCO=2.5V,和VSWING(LVDS)=380mV進入等式2-4并四舍五入到最接近的1%如圖所示,發現RS=61.9歐姆和RDIV=63.4歐姆的值在圖4中,350mV的典型LVDS電壓擺幅增加到380mV在50英寸末端附近以311Mb/s的數據速率抵消趨膚效應損失多點線。

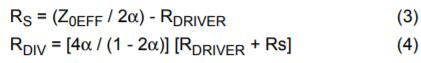

CSLEW增加了Virtex-E多點驅動器的上升時間。通常情況下,LVDS的10-90%上升時間為500ps。使用CSLEW,所需的上升時間為增加到大約1ns。使用等效的差分半電路圖4,(RDIV->RDIV/2,CSLEW->2CSLEW),驅動點阻抗為2CSLEW是REQ//RT/2=REQ/2。RC時間常數是:(2CSLEW)(REQ/2)=REQCSLEW。

通過設置τ,RC時間常數,等于原始LVDS上升10-90%屆時,新的10-90%的上升時間將近1ns。CSLEW的值是

計算公式為:

CSLEW=τ/REQ(5)

將τ=500ps和REQ=22歐姆代入公式5并進行四舍五入

得到最接近的10%值,得到CSLEW=27pF的值,如圖所示圖4。

差分晶振是石英水晶組件算是最高級的一種,使用的效果和意義是非常大的,而且隨著全球大范圍的重視科技,發展科技,產品變得更多功能化,復雜化,部分中高端產品需要差分晶體振蕩器這種高性能,高穩定,高可靠性的頻率元件支持。而且還在保障低電壓效能,常用的是1.8~3.3V之間,耗能是非常低的,精準的識別小信號,分析處理“雙極”信號,可能幫助產品阻抗外界的干擾。

相關技術支持

- FCD-Tech石英晶體F2520A-30-50-K-30-F-34.000MHz術語和定義理論

- ECS許多應用需要石英振蕩器ECS-100AX-110.5和其他定時解決方案

- Abracon超小型ABS05-32.768KHZ-T音叉晶體專為節能MCU而優化

- Bliley壓控晶振BVCS5-24.000MHZMDN-ABCBT如何工作?

- Microchip用于嵌入式系統的新型PIC18F06Q20微控制器(MCU)

- Golledge下一代GSRFTA0942A頻率控制5G網絡的解決方案

- CTS最新推出的OCXO完美應用于各個領域

- 遙遙領先的Harmony Electronics Corp.用水晶增強安全駕駛

- 了解遙遙領先的SIWARD希華晶體振蕩器

- 領先全球Skyworks晶振為下一代Wi-Fi 6/6E設備提供前所未有的能效

手機版

手機版