LVDS差分晶振的直流耦合終端建議

在實際應用中LVDS輸出差分晶振的作用是非常大的,因為這是一種低電壓,低功耗的差分信號傳輸模式,可以用在接口,當然也可以搭載于石英晶振身上.LVDS是振蕩器常見的輸出邏輯之一,通常都是用來匹配SPXO,VCXO,OCXO還有MEMS等多種不同的石英晶體振蕩器,使這些晶振具備低插損,低電平,低相位抖動,低相位噪聲,低衰減等優良電氣特性.適用無線網絡,光纖蜂窩,導航定位,人造衛星,航空航天,基建設備,無線基站,雷達,控制系統,電信通信,船舶呼救系統等高端產品使用.

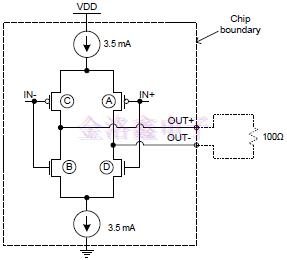

圖8:LVDS驅動器輸出結構

LVDS是一種高速數字接口,適用于需要低功耗和高抗噪性的許多應用.LVDS輸出使用具有低電壓擺幅的差分信號以高速傳輸數據.圖8顯示了LVDS驅動器的輸出結構,包括3.5mA標稱電流源,通過開關網絡連接到差分輸出,有時稱為”H”開關.輸出通常連接到100Ω差分傳輸線,端接接收器輸入端的100Ω電阻.電阻值與傳輸線的阻抗相匹配,并為信號提供電流路徑.驅動器包括用于將共模設置為1.2V的電路,無論VDD如何.因此,不需要將驅動器外部偏置到任何特定電壓.此外,低電壓差分晶振可以連接到任何LVDS輸入,而無需考慮振蕩器的實際電源電壓.

信號切換由四個標有A,B,C和D的晶體管完成.由于接收器的阻抗通常較高,因此來自驅動器的幾乎所有電流都流過100Ω電阻,導致接收器之間的電壓差為350mV投入.在圖8中,當信號IN為低電平時,晶體管A和B導通;電流流過晶體管A和100Ω電阻,然后通過晶體管B返回.當信號IN為高電平時,晶體管C和D導通;電流流過晶體管C和100Ω電阻,然后通過晶體管D返回,從而在接收器兩端產生-350mV的電壓.從接收器的角度來看,流過終端電阻器的電流方向決定了是否記錄了正差分電壓或負差分電壓.正差分電壓表示邏輯高電平,而負差分電壓表示邏輯低電平.

晶振直流耦合應用的終端建議

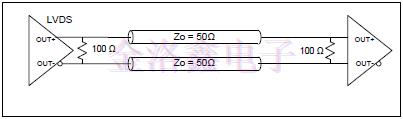

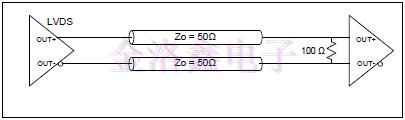

具有100Ω差分走線的LVDS接口通常在接收器端端接,在接收器的差分輸入端有一個100Ω電阻(見圖9).有些接收器采用100Ω片上電阻,無需外部端接.

圖9:負載時的LVDS單直流端接

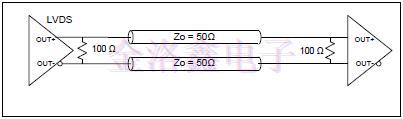

對于大多數應用,負載上的單個終端就足夠了.在負載反射系數相對較高的情況下,雙端接布置可以減少整個往返(參見圖10).在源極和負載兩端都有一個100Ω電阻,輸出驅動器的等效電阻降至50Ω,導致輸出信號擺幅減半.

附錄A:傳輸線終端阻抗匹配有關單端和雙端設備使用的更多信息.

圖10:LVDS雙直流端接

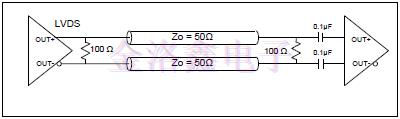

交流耦合應用的終端建議

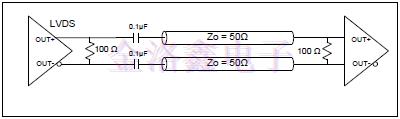

如果LVDS驅動器和接收器使用不同的共模電壓工作,建議使用AC端接.電容器用于阻斷來自驅動器的直流電流路徑,因此接收器必須實現其自己的輸入偏置電路.AC耦合可以配置為負載的單個終端,或者配置為雙終端.單端接如圖11所示.對于單端和雙端,交流耦合電容可放置在負載終端電阻之前(如圖12所示)或之后(如圖13所示).

圖11:負載時的LVDS單AC端接

(圖12和圖13)中所示的雙端子僅在AC耦合電容器的位置上有所不同.圖12中的電容器通過流過差分電阻一半的共模電流充電,相當于50Ω.圖13中的電容器通過接收器輸入電阻的電流充電,接收器輸入的電阻可以在幾十千歐的范圍內.在時鐘啟動期間,圖12所示的電容充電速度比圖13所示的快得多.因此,接收器可以更快地獲得有效的時鐘信號.如果快速時鐘啟動很重要,則最好采用圖12所示的配置.

圖12:LVDS雙交流端接,電容器靠近電源

在數據傳輸應用中,圖13中所示的配置可能更有利.由于LVDS輸出晶振較高的RC時間常數,它可以維持較長的1和0的數據序列,而不會出現明顯的電壓下降.

圖13:LVDS雙AC端接,電容器靠近負載

LVDS輸出的有源晶振要極端惡劣的環境下,也能保持穩定的振蕩功能,不會受周圍溫度的影響而發生頻率漂移的現象.打個比方,如果智能手機里有一顆LVDS晶振,那么即使到零下十幾或二十幾的低溫環境,這部手機也不會失效故障,這就是為什么要用高性能晶體振蕩器的原因.

手機版

手機版