精密振蕩器為高速串行通信鏈路實現了CDR

網絡與通信已經成為城市最基本的基礎建設,現代人也離不開信號網絡,一顆高精密性的石英晶體振蕩器,可以使網絡模塊設備,電信,高速串行通信鏈路等產品性能提升.現在普遍都是使用4G網絡,但是目前5G通信即將覆蓋,許多地方開始更換5G的無線基站,5G不僅僅是比4G多一個G而已,其速度將會是上一代4G的百倍.而且5G主要是應用到高端的操作,例如高速串行通信鏈路,時鐘數據恢復,遠程操控等.

時鐘數據恢復(CDR)的應用在電信,光收發器,數據和存儲區域網絡以及無線產品中比比皆是.隨著設計需要更大的帶寬以及分配和頻譜帶寬使用的增加,CDR技術的優勢變得越來越重要.此外,供應商及其產品正在從并行轉換為串行接口,用于系統級和板級接口.近年來,CDR技術的使用越來越多,因為需要在背板上處理更寬的并行總線寬度,同時管理接收器的時鐘和數據偏差.此外,路由這些信號可能很困難,因為它們消耗電路板空間和功率,并且需要多層路由方案來管理信號和線路終端.使用高位寬數據總線產生的EMI也是一個問題.

由于新通信技術的出現,電信號處理的改進以及跨FR-4和背板,光學和無線媒體發送多千兆位電信號的需求,CDR非常重要.在傳輸之前組合時鐘和數據的通信技術并不新鮮.時鐘和數據的組合確保時鐘和數據信號始終同時到達.然而,訣竅是接收器處的時鐘和數據的分離.這是由CDR電路完成的.將數據從并行格式轉換為串行格式或反之亦然的產品稱為串行器/解串器(或簡稱”SerDes”).這些產品通常具有CDR塊以對串行數據流進行反序列化.

本文探討了在高速串行通信鏈路應用中實現成功CDR所需的CDR組件模塊.提供了關于如何通過鏈路轉換和重新捕獲數據的典型高速串行通信鏈路的概述.關于一般CDR拓撲討論了不同的CDR方案.此外,還特別注意參考石英振蕩器在鏈路的發送側和接收側的作用.

高速串行通信中的時鐘和數據恢復

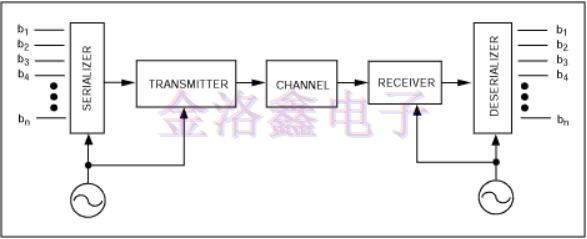

圖1提供了高速串行通信鏈路的基本圖.并行數據(比特b1,b2,b3,...bn)以頻率ft到達傳輸串行器.在串行器內,數據從并行格式轉換為串行格式.開發串行比特流,其最小比特率等于nxft,其中n是并行數據比特的總數.得到的頻率(比特率)可以高于ft取決于數據是否被編碼以滿足誤碼率(BER)性能的信道要求或者在接收側CDR提供豐富的轉換內容.Reed-Solomon前向糾錯(FEC)和8B10B編碼分別是信道編碼或在接收CDR處創建豐富轉換內容的每個示例.然后準備該串行數據以便傳輸到信道并發送到接收器,最后到達解串器.該基本通信模塊適用于數據,無論是通過光纖,空中還是跨背板傳輸.

圖1.時鐘和數據恢復是高速串行通信鏈路的基礎.

時序(時鐘)在CDR應用中至關重要.在系統設計期間,設計者確定如何將數據從并行格式驅動到串行格式,以便通過具有發送信號的未決信道失真的信道進行發送和接收.最大限度地降低設計降級對數據信號的影響對于保護信噪比和保持BER性能非常重要.例如,在背板的數字傳輸方案中,系統的抖動性能非常重要,因為高速電信號穿過各種長度(FR-4和背板),從而導致信號電平和時變信號降級扭曲.

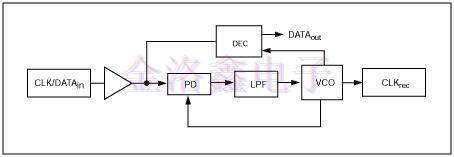

時鐘數據恢復的核心是基于鎖相環(PLL)的電路,在某些情況下可以基于數字.圖2是可用于圖1所示通信鏈路的串行器或發送側的基本PLL框圖.PLL模塊包括相位頻率檢測器(PD),濾波器(LPF),壓控晶振(VCO)和分割鏈(1/n).分頻鏈用于向PD提供可比較的頻率輸入.通過這種方式,VCO的輸出與非常穩定的參考輸入VREF相位對齊.該PLL模塊的目的是將參考頻率乘以固定量(n),這將是VCO的固有頻率.在大多數情況下,VREF將是基于石英的,提供高度的穩定性和準確性以及相位噪聲特性.此外,根據所需的應用或系統要求,該參考可以是溫度補償或電壓補償.在基于SONET的應用程序中,此引用可能滿足某個層級(即層級別3,3E或4).

圖2.時鐘乘法應用由PLL驅動.

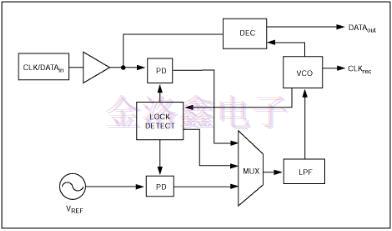

在接收端,CDRPLL模塊具有略微不同的外觀,以滿足檢索時鐘和數據的需要.如圖3所示,組合的時鐘/數據信號通過緩沖器進入PLL模塊,緩沖器為兩條不同的路徑供電.一條路徑饋送數據決策(DEC)塊,而第二條路徑饋送時鐘恢復塊.時鐘恢復模塊看起來非常像圖2的PLL模塊減去1/n模塊.來自VCO貼片振蕩器的恢復時鐘用作DEC的采樣輸入,反饋到相位-頻率檢測器,并且還用于向下游提供系統時序要求.在圖1的情況下,該恢復的時鐘被分頻為并行時鐘頻率以驅動解串器塊.

圖3.基本PLL模塊的修改用于實現CDR電路.

時鐘/數據恢復中的參考振蕩器

圖中所示的參考振蕩器說明了VCO被施加到振蕩器的輸入端.該電壓控制由LPF級建立.通常,VCO或壓控晶體振蕩器(VCXO)可用作環路振蕩器,如圖3所示.主要作用是,環路振蕩器需要跟蹤輸入時鐘/數據的頻率偏差.此外,它還為CDR(解串器)下游的其他組件提供此時鐘.這是通過LPF的輸出實現的,LPF驅動VCO或VCXO晶振的電壓控制輸入.

在用于電信,無線和數據通信的CDR應用中,輸入數據信號加上時鐘應具有相對穩定的頻率特性.這假設發送時鐘滿足一定的精度和穩定性規范.在接收方面,設計排除了最小和最大精度/穩定性.如果傳輸時鐘頻率預計為規定頻率的±50ppm,則接收時鐘的頻率調整能力至少為±50ppm.但是,出于設計目的,考慮頻率調整能力略大于±50ppm.這種擴展的頻率調整功能可以適應信道的任何額外信號頻率失真或通信中斷.

盡管PLL試圖驅動靜態條件,意味著已經建立了頻率鎖定,但可能存在電壓控制輸入可能以高于期望的速率移動的條件.LPF帶寬決定了PLL可以保持鎖定的最大速率.最終,接收VCO(或VCXO)的作用是跟蹤和再現恢復的時鐘.在沒有數據/時鐘輸入到CDR的情況下,CDR在指定時間內需要為任何下游通信要求(即解串器)提供參考信號.

在某些應用中,將使用VCO/VCXO組合.在圖4中,VCO/VCXO允許共同CDR配置至少有兩個好處.首先,VCXO的添加允許快速調節VCO頻率以匹配預期時鐘/數據信號的頻率.選擇VCXO頻率以匹配預期的時鐘頻率范圍.例如,寬帶VCO可能需要數千個樣本才能鎖定輸入數據流.增加LV-PECL壓控晶振和鎖定檢測電路可確保VCO保持一定的工作頻率,并有助于在啟動條件下提供更可預測的鎖定時間.其次,如果時鐘/數據輸入在較長時間內丟失,則添加VCXO會很有幫助.在沒有時鐘/數據信號的情況下,系統會參考非常穩定的石英振蕩器(VREF)提供保持,直到時鐘/數據信號從信號丟失(LOS)中恢復.保持是一種規范,適用于參考時鐘在一段時間內保持一定精度的能力(例如,24小時內為±4.6ppm).

圖4.對基本CDR模塊的修改可以輕松鎖定傳入的時鐘/數據流.

各種解決方案可解決時鐘/數據恢復和重定時,串行器和解串器,時鐘發生器以及用于通信應用的TCXO晶振.這些器件允許設計人員開發頻率范圍從10MHz到10GHz的電路,并支持從GSM到OC-192及以上的應用.隨著設計越來越需要更大的帶寬,CDR技術非常適用于電信,光收發器,數據和存儲區域網絡以及無線應用.

相關技術支持

- FCD-Tech石英晶體F2520A-30-50-K-30-F-34.000MHz術語和定義理論

- ECS許多應用需要石英振蕩器ECS-100AX-110.5和其他定時解決方案

- Abracon超小型ABS05-32.768KHZ-T音叉晶體專為節能MCU而優化

- Bliley壓控晶振BVCS5-24.000MHZMDN-ABCBT如何工作?

- Microchip用于嵌入式系統的新型PIC18F06Q20微控制器(MCU)

- Golledge下一代GSRFTA0942A頻率控制5G網絡的解決方案

- CTS最新推出的OCXO完美應用于各個領域

- 遙遙領先的Harmony Electronics Corp.用水晶增強安全駕駛

- 了解遙遙領先的SIWARD希華晶體振蕩器

- 領先全球Skyworks晶振為下一代Wi-Fi 6/6E設備提供前所未有的能效

手機版

手機版