SiTime晶振的MEMS技術起源于博世和斯坦福大學。在我們的創始人創立SiTime之前,他們花了數年時間,在德國的博世和加州的帕洛阿爾托研發挽救生命的MEMS解決方案。我們已經向世界各地的客戶提供了超過7億部份的產品,在MEMS的時間安排上有90%的份額,并且每年都在以超過50%的速度增長。SiTime是兆大公司(東京證券交易所:6875)的獨立子公司。SiTime于2013年進入智能手機市場,第一個是移動電話的MEMS振蕩器,現在可穿戴設備和物聯網應用正在快速增長。

我們讓oem廠商和ODMs都很容易使用SiTime貼片晶振。我們的QFN振蕩器是100%的替代石英振蕩器,而不需要任何板上的改變。另外,我們的可編程架構使最靈活的產品具有更多的特性和超快的交貨期。SiTime解決方案是一個很容易的選擇——一旦我們的客戶使用SiTime產品,他們很少會回到quartz。超小型有源晶振,低電壓晶體振蕩器,SiT1552晶振

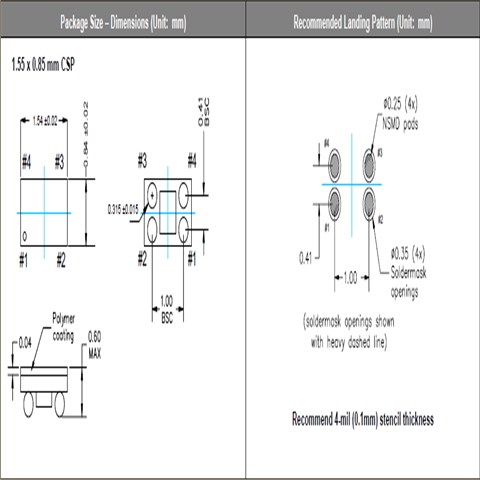

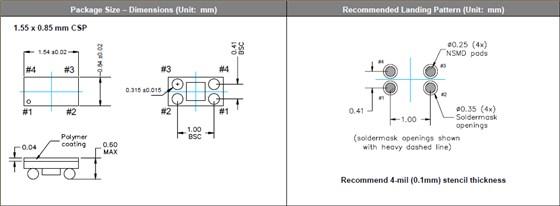

SiTime晶振,溫補晶振,SiT1552晶振.是針對電池供電應用而優化的超小型,超低功耗32.768 kHz TCXO。 SiTime的硅MEMS技術使全球最小的封裝和芯片級封裝(CSP)中的首款32 kHz TCXO成為可能。典型的內核電源電流僅為1μA。與標準振蕩器不同的是,SiT1552具有NanoDrive™(工廠可編程輸出),可降低電壓擺幅以最大限度地降低功耗。TCXO頻率穩定性SiT1552在多個溫度點進行出廠校準(微調),以確保在整個溫度范圍內具有極高的穩定性。

SiTime貼片晶振晶片邊緣處理技術:貼片晶振是晶片通過滾筒倒邊,主要是為了去除石英晶振晶片的邊緣效應,在實際操作中機器運動方式設計、滾筒的曲率半徑、滾筒的長短、使用的研磨砂的型號、多少、填充物種類及多少等各項設計必須合理,有一項不完善都會使晶振晶片的邊緣效應不能去除,而石英晶振晶片的諧振電阻過大,用在電路中Q值過小,從而電路不能振動或振動了不穩定。

|

SiTime晶振 |

標示 |

SiT1552晶振 |

晶振基本信息對照表 |

|

標準范圍 |

f0 |

32.768KHz |

|

|

電源電圧 |

Vcc |

+1.5V~3.63V |

|

|

輸出電流 |

Icc |

3.5 mA max. |

Vcc1.8V |

|

頻率負載 |

L_CMOS |

15pF |

LVCMOS出力 |

|

標準頻率偏差 |

f_tol |

±5.0×10-6 max.

|

初期偏差、 |

|

輸出電壓 |

V |

VOH:Vcc×90% min.VOL:Vcc×10% max. |

|

|

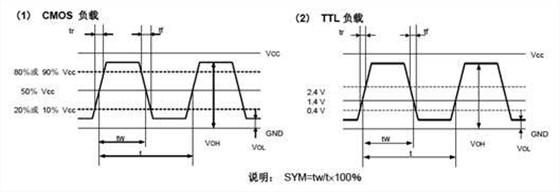

對稱 |

SYM |

40%~60% |

50% Vcc |

|

標準時間 |

tr/tf |

12 ns max.(1.8~80MHz) |

10%Vcc~90%、L_CMOS=15pF |

噪音

在電源或輸入端上施加執行級別(過高)的不相干(外部的)噪音,可能導致會引發32.768K溫補晶振功能失常或擊穿的閉門或雜散現象。

電源線路

電源的線路阻抗應盡可能低。SiTime晶振,溫補晶振,SiT1552晶振

輸出負載

建議將輸出負載安裝在盡可能靠近石英振蕩器的地方(在20 mm范圍之間)。

未用輸入終端的處理

未用針腳可能會引起噪聲響應,從而導致非正常工作。同時,當P通道和N通道都處于打開時,電源功率消耗也會增加;因此,請將未用輸入終端連接到VCC 或GND。

熱影響

重復的溫度巨大變化可能會降低受損害的32.768K晶體振蕩器的產品特性,并導致塑料封裝里的線路擊穿。必須避免這種情況。

安裝方向

進口晶體振蕩器的不正確安裝會導致故障以及崩潰,因此安裝時,請檢查安裝方向是否正確。超小型有源晶振,低電壓晶體振蕩器,SiT1552晶振

通電

不建議從中間電位和/或極快速通電,否則會導致導航儀有源晶振無法產生振蕩和/或非正常工作。

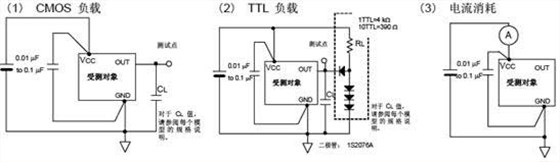

輸出波形與測試電路

1.時序表

2.測試條件

(1)電源電壓

超過 150µs,直到電壓級別從 0 %達到 90 % 。超小型有源晶振,低電壓晶體振蕩器,SiT1552晶振

電源電壓阻抗低于電阻 2Ω。

(2)其他

輸入電容低于 15 pF

5倍頻率范圍或更多測量頻率。

鉛探頭應盡可能短。

測量頻率時,探頭阻抗將高于 1MΩ。當波形經過振蕩器的放大器時,可同時進行測量。

(3)其他

CL包含探頭電容。

應使用帶有小的內部阻抗的電表。

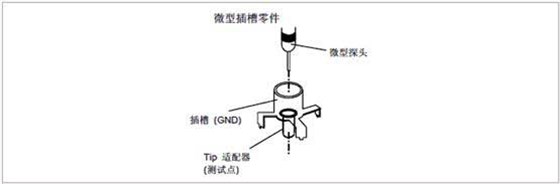

使用微型插槽,以觀察波形。

(請勿使用該探頭的長接地線。)SiTime晶振,溫補晶振,SiT1552晶振

3.測試電路