SiTime在MEMS(微機電系統)技術、模擬CMOS電路設計和開發方面具有深厚的技術專長,并具有成本效益的組裝和測試。這些專業技術的結合,都是在SiTime內部進行的,在計時行業中是獨一無二的,推動創新的速度要比quartz快得多。除了MEMS和模擬電路的專業知識外,SiTime還具備以優異的質量和可靠性交付大量產品的能力。這種能力來自于我們的裝配、測試和校準技術,使我們能夠提供一個完全集成的解決方案,完全可以與行業標準的腳印相兼容。

SiTime的基于內存的硅計時解決方案受益于廣泛的應用。作為石英設備的替代品,SiTime的振蕩器和時鐘發生器已經成功地將石英計時工業轉化為硅基產品。通過一個全新的全硅平臺,SiTime有著卓越的歷史成就。我們快速的技術突破是通過利用硅技術的優勢,結合了數十年的MEMS諧振器經驗和內部模擬技術來實現的。半導體公司正在將我們的硅MEMS諧振器集成到他們的足球/asics中,從而完全消除外部時鐘,簡化系統設計。

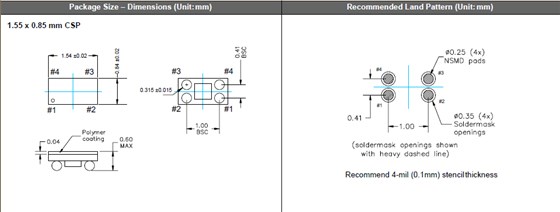

SiTime晶振,32.768K有源晶振,SiT1532晶振.是全球最小,功耗最低的32.768kHz振蕩器,針對移動和其他電池供電應用而優化。SiTime的硅MEMS技術實現了最小尺寸和芯片級封裝。與現有的2.0*1.2mm SMD XTAL封裝相比,該器件可將32 kHz占用空間減少85%。與XTAL不同,SiT1532振蕩器輸出實現了更大的元件貼裝靈活性,并消除了外部負載電容,從而節省了額外的元件數量和電路板空間。

SiTime晶振的真空封裝技術:是指石英晶振在真空封裝區域內進行封裝。1.防止外界氣體進入組件體內受到污染和增加應力的產生;2.使晶振組件在真空下電阻減小;3.氣密性高。此技術為研發及生產超小型、超薄型石英晶振必須攻克的關鍵技術之一。

|

SiTime晶振 |

標示 |

SiT1532晶振 |

晶振基本信息對照表 |

|

標準范圍 |

f0 |

32.768KHz |

|

|

電源電圧 |

Vcc |

+1.5V~3.63V |

|

|

輸出電流 |

Icc |

3.5 mA max. |

Vcc=3.3V |

|

頻率負載 |

L_CMOS |

15pF |

LVCMOS出力 |

|

標準頻率偏差 |

f_tol |

±10、±20×10-6 max.

|

初期偏差、 |

|

輸出電壓 |

V |

VOH:Vcc×90% min.VOL:Vcc×10% max. |

|

|

對稱 |

SYM |

40%~60% |

50% Vcc |

|

標準時間 |

tr/tf |

12 ns max.(1.8~80MHz) |

10%Vcc~90%、L_CMOS=15pF |

噪音

在電源或輸入端上施加執行級別(過高)的不相干(外部的)噪音,可能導致會引發功能失常或擊穿的閉門或雜散現象。

電源線路

電源的線路阻抗應盡可能低。

輸出負載

建議將輸出負載安裝在盡可能靠近石英振蕩器的地方(在20 mm范圍之間)。

未用輸入終端的處理

未用針腳可能會引起噪聲響應,從而導致非正常工作。同時,當P通道和N通道都處于打開時,電源功率消耗也會增加;因此,請將未用輸入終端連接到VCC 或GND。

熱影響

重復的溫度巨大變化可能會降低受損害的有源晶振的產品特性,并導致塑料封裝里的線路擊穿。必須避免這種情況。

安裝方向

進口晶體振蕩器的不正確安裝會導致故障以及崩潰,因此安裝時,請檢查安裝方向是否正確。

通電

不建議從中間電位和/或極快速通電,否則會導致有源晶體無法產生振蕩和/或非正常工作。

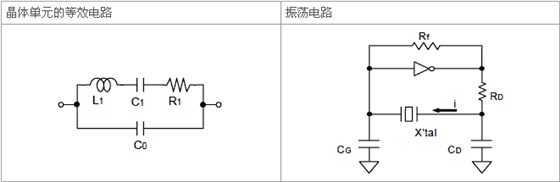

設計振蕩回路的注意事項

1.驅動能力

驅動能力說明振蕩晶體單元所需電功率,其計算公式如下:

驅動能力 (P) = i2_Re

其中i表示經過晶體單元的電流,

Re表示晶體單元的有效電阻,而且 Re=R1(1+Co/CL)2。

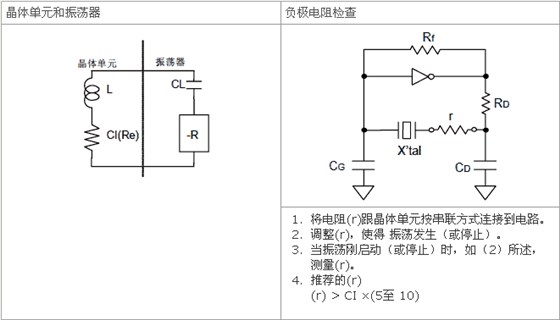

2.振蕩補償

除非在振蕩電路中提供足夠的負極電阻,否則會增加振蕩啟動時間,或不發生振蕩。為避免該情況發生,請在電路設計時提供足夠的負極電阻。

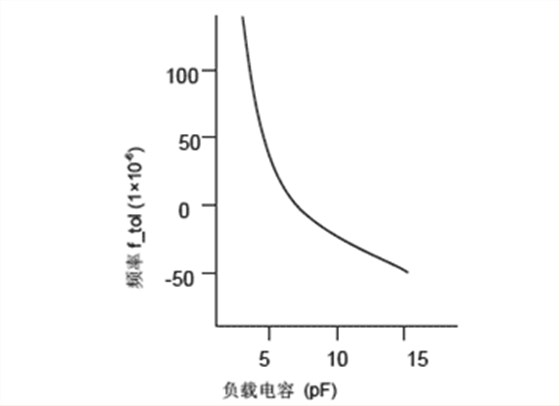

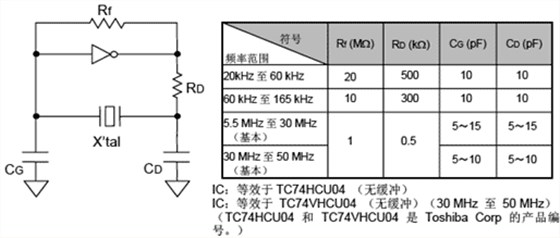

3.負載電容

如果振蕩電路中負載電容的不同,可能導致振蕩頻率與設計頻率之間產生偏差,如下圖所示。電路中的負載電容的近似表達式 CL≒CG × CD / (CG+CD) + CS。

其中CS表示電路的雜散電容。

頻率和負載電容特征圖器

振蕩回路參數設置參考

SiTime晶振,有源晶振,SiT1533晶振

SiTime晶振,有源晶振,SiT1533晶振 RTC晶振,SM33K進口晶振,PLETRONICS晶振,SM3344KE-32.768K,2520有源貼片

RTC晶振,SM33K進口晶振,PLETRONICS晶振,SM3344KE-32.768K,2520有源貼片